Understanding the future of AI-driven semiconductors is essential for anyone navigating the rapidly evolving landscape of computing, from data centers to edge devices. These specialized chips, designed specifically to accelerate artificial intelligence workloads, are moving beyond mere accelerators to become the foundational engines of the digital economy. As AI models grow exponentially in size and complexity, the semiconductor industry is undergoing a profound architectural shift, moving away from general-purpose computing towards highly specialized, heterogeneous systems. This transition promises unprecedented efficiency and capability but also introduces significant challenges in design, manufacturing, and integration. Consequently, the trajectory of AI-driven semiconductors will dictate the pace of innovation across industries, from autonomous vehicles and healthcare diagnostics to natural language processing and scientific discovery.

Key Takeaways

- AI-driven semiconductors are evolving from accelerators to full-system-on-chip (SoC) architectures integrating memory, networking, and specialized cores.

- Specialized architectures like neuromorphic and in-memory computing are emerging to overcome the limitations of traditional von Neumann designs.

- Advanced packaging technologies (Chiplets, 3D-IC) are becoming as critical as transistor scaling for performance gains.

- The AI chip market is fragmenting, with domain-specific designs for cloud, edge, and endpoint applications.

- Software-hardware co-design and robust AI-specific toolchains are now mandatory for performance and developer adoption.

- Supply chain resilience and geopolitical factors are heavily influencing the design and manufacturing strategies for AI semiconductors.

The Architectural Revolution: Beyond the GPU

For years, Graphics Processing Units (GPUs) have been the workhorses of AI training and inference, thanks to their massively parallel architecture. However, understanding the future of AI-driven semiconductors requires looking beyond this initial phase. The next generation is characterized by heterogeneous integration and domain-specific architectures. Companies are designing chips that combine different types of processing cores—such as tensor cores for matrix math, vector units, and scalar CPUs—onto a single die or package. This approach allows for more efficient task allocation, drastically reducing the power and latency associated with shuttling data between discrete components. For instance, Google’s Tensor Processing Unit (TPU) and Amazon’s Inferentia are prime examples of this trend, offering tailored performance for specific AI model types and cloud workloads.

Furthermore, the traditional von Neumann bottleneck, where the speed of computation is limited by the rate data can move between memory and the processor, is a critical target. Consequently, new architectures are blurring the lines between memory and compute. In-memory computing and near-memory computing designs place processing elements within or adjacent to memory arrays, slashing data movement energy. Research from institutions like IBM and imec is pushing this frontier with analog compute-in-memory using non-volatile memory technologies. Meanwhile, neuromorphic computing chips, which mimic the brain’s neural structure for ultra-low-power, event-driven processing, are moving from labs to pilot deployments for sensor-driven edge AI applications.

Specialization for the Cloud, Edge, and Endpoint

The one-size-fits-all chip is disappearing. The architectural future is deeply fragmented based on deployment environment. Cloud data center chips prioritize raw throughput and scalability for training massive models. They increasingly incorporate high-bandwidth memory (HBM) and dedicated on-chip networking like NVIDIA’s NVLink. Conversely, edge AI semiconductors, for use in smart cameras, robots, or gateways, must balance performance with stringent power and thermal envelopes. These often use system-on-chip (SoC) designs that integrate the AI accelerator, CPU, and I/O controllers. Finally, endpoint AI, for smartphones, wearables, and IoT devices, demands extreme power efficiency, leading to tiny, highly optimized neural processing units (NPUs) that can operate in the milliwatt range.

Advanced Packaging: The New Moore’s Law

As transistor scaling at the nanometer level becomes exponentially more difficult and costly, the industry’s focus is shifting towards advanced packaging as a primary lever for performance. Understanding the future of AI-driven semiconductors is impossible without appreciating the role of 2.5D and 3D integration. Technologies like silicon interposers, through-silicon vias (TSVs), and hybrid bonding allow multiple silicon dies (chiplets) to be combined into a single, high-performance package. This “chiplet” model enables a modular approach, where a company can design or procure best-in-class chiplets for I/O, memory, and compute, and integrate them efficiently.

“The future of high-performance computing is less about a single monolithic die and more about the art of heterogeneous integration. Advanced packaging is now a first-order design consideration, not an afterthought,” notes a senior engineer at a leading semiconductor research consortium.

This paradigm reduces time-to-market and cost, as smaller dies have higher yield rates. It also facilitates the creation of heterogeneous systems that combine logic dies manufactured at the most advanced node (e.g., 3nm) with memory dies or analog/RF components made on older, more economical nodes. Major players like Intel (with its Foveros and EMIB technologies), TSMC (with its CoWoS platform), and AMD have made advanced packaging a cornerstone of their AI chip strategies. The ability to stack memory directly on top of a processor in a 3D configuration, for example, offers bandwidth improvements orders of magnitude greater than what traditional PCB connections can provide, directly addressing the data movement challenge central to AI performance.

Market Dynamics and the Geopolitical Landscape

The race for AI semiconductor supremacy is not just a technical challenge; it’s a geopolitical and economic battleground. The market is diversifying beyond the early dominance of a few players. While NVIDIA continues to lead in the data center accelerator space, a host of companies are competing fiercely. These include large cloud providers (Google, Amazon, Microsoft designing their own chips), established semiconductor firms (Intel, AMD), and a vibrant ecosystem of startups focusing on specific niches like AI inference or neuromorphic architectures. This competition is driving rapid innovation but also leading to fragmentation in software toolchains and standards.

Simultaneously, supply chain security has become paramount. The concentration of advanced semiconductor manufacturing in specific geographic regions, notably Taiwan and South Korea, poses a significant risk. Nations are investing heavily in building sovereign capabilities. The U.S. CHIPS and Science Act, the European Chips Act, and similar initiatives in Japan and India are funneling hundreds of billions of dollars into domestic R&D and manufacturing. This push for supply chain resilience will likely lead to a more distributed, albeit potentially less economically efficient, global manufacturing footprint. Furthermore, export controls on advanced AI chips and manufacturing equipment are shaping the strategies of companies worldwide, forcing design innovations that work within constrained technology boundaries.

The Software-Hardware Co-Design Imperative

In this fragmented landscape, hardware alone is not enough. The winning AI-driven semiconductors will be those with the most robust, accessible software stacks. The era of software-hardware co-design is here. Developers will not adopt a new chip architecture if programming it requires Herculean effort. Therefore, companies are investing heavily in compilers, libraries, and frameworks that abstract the hardware complexity. Open standards like MLPerf for benchmarking are also critical for fair comparison and driving performance improvements. The software ecosystem, perhaps even more than the transistor density, will determine the long-term viability of any new AI semiconductor architecture.

Energy Efficiency: The Ultimate Constraint

Perhaps the most pressing challenge in understanding the future of AI-driven semiconductors is the energy problem. Training large AI models consumes staggering amounts of power, and projections suggest this demand could become unsustainable. Future chips must deliver massive improvements in performance per watt. This drives innovation at every level: new transistor materials (like RibbonFET or Gate-All-Around), lower-voltage operation, architectural tricks like sparsity exploitation (skipping zero-value computations), and the aforementioned in-memory computing. Moreover, the entire data center is being rethought around the AI chip, with liquid cooling becoming standard and power delivery networks undergoing radical redesigns.

The focus on efficiency is also pushing AI towards mixed-precision computing. Not all calculations in an AI model need 32-bit or 16-bit floating-point precision. Many can be done in 8-bit integers or even lower, with specialized hardware to support these data types. Some research is exploring 4-bit and 1-bit (binary) neural networks, which could lead to another order-of-magnitude leap in efficiency. The AI semiconductors of the future will likely feature dynamic precision scaling, adapting the numerical format on the fly based on the layer of the neural network being processed to optimize both accuracy and power consumption.

The Rise of Photonic and Quantum-Inspired Chips

Looking further ahead, entirely new physical paradigms are entering the conversation. Photonic (optical) computing uses light instead of electrons to perform calculations, offering the potential for ultra-high speed and minimal heat generation, especially for linear algebra operations fundamental to AI. Several startups are developing photonic chips for AI inference, promising latency and bandwidth benefits for specific applications. While fully optical general-purpose computing remains distant, hybrid electro-optical interconnects and co-processors are likely to appear within the next decade to alleviate I/O bottlenecks.

Similarly, quantum-inspired algorithms run on classical hardware but use principles from quantum computing to solve optimization problems more efficiently. Specialized semiconductors could be built to accelerate these algorithms. While true fault-tolerant quantum computing for AI is still a long-term prospect, the cross-pollination of ideas is influencing classical chip design, particularly in areas like analog AI computing and novel approaches to optimization. Keeping an eye on these frontier technologies is crucial for a complete picture of the semiconductor roadmap.

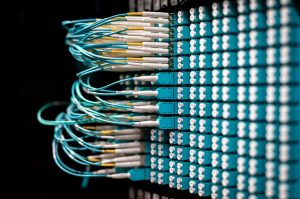

Implications for Telecom and Network Infrastructure

The impact of AI-driven semiconductors extends powerfully into telecom and network infrastructure. The rollout of 5G-Advanced and 6G networks will be fundamentally enabled by AI chips embedded at every layer. Radio Access Networks (RAN) will use AI for real-time beamforming, spectrum management, and network slicing optimization. These tasks require low-latency inference at the edge, driving demand for specialized, power-efficient AI SoCs in base stations. Furthermore, the core network will leverage AI for security threat detection, traffic routing, and predictive maintenance. The integration of AI processors directly into network switches and routers will create intelligent, self-optimizing data planes.

This convergence also means telecom equipment providers and operators are becoming significant consumers and even designers of AI semiconductors. They need chips that meet rigorous reliability standards, operate in harsh environments, and support specific telecom protocols. Consequently, partnerships between semiconductor firms and telecom giants are deepening, leading to another category of domain-specific AI chips tailored for the unique demands of future mobile and fixed networks.

Conclusion

Understanding the future of AI-driven semiconductors reveals a field in explosive, multi-dimensional evolution. The journey is moving from general-purpose hardware running AI software to fundamentally new silicon architectures co-designed with the algorithms they are meant to run. Success will be determined not just by transistor counts, but by system-level innovation in packaging, energy efficiency, and software ecosystems. As these specialized chips proliferate into every corner of the digital and physical world, they will catalyze breakthroughs we can only begin to imagine.

The path forward is fraught with challenges—from technical hurdles in materials science to geopolitical tensions over supply chains. Yet, the imperative is clear: the semiconductor industry must continue to innovate at a breakneck pace to sustain the AI revolution. For businesses and technologists, staying informed on these trends is no longer optional; it is essential for strategic planning and competitive advantage. The question is no longer if AI will transform semiconductors, but how quickly and profoundly this transformation will reshape our technological capabilities.